### FAIRCHILD

SEMICONDUCTOR

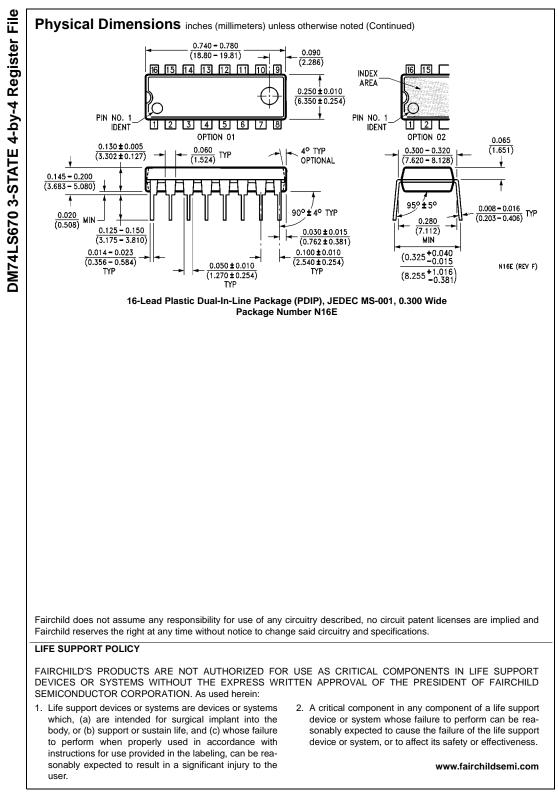

# DM74LS670 3-STATE 4-by-4 Register File

#### **General Description**

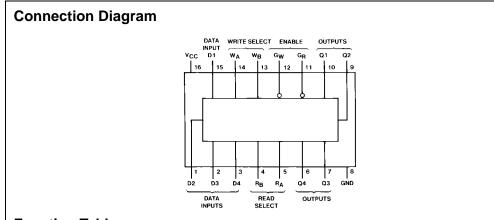

These register files are organized as 4 words of 4 bits each, and separate on-chip decoding is provided for addressing the four word locations to either write-in or retrieve data. This permits writing into one location, and reading from another word location, simultaneously.

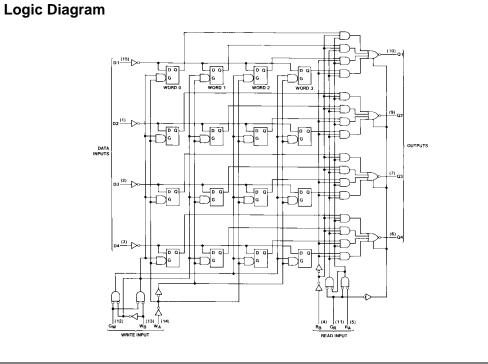

Four data inputs are available to supply the word to be stored. Location of the word is determined by the write select inputs A and B, in conjunction with a write-enable signal. Data applied at the inputs should be in its true form. That is, if a high level signal is desired from the output, a high level is applied at the data input for that particular bit location. The latch inputs are arranged so that new data will be accepted only if both internal address gate inputs are HIGH. When this condition exists, data at the D input is transferred to the latch output. When the write-enable input,  $G_W$ , is HIGH, the data inputs are inhibited and their levels can cause no change in the information stored in the internal latches. When the read-enable input,  $G_R$ , is HIGH, the data outputs are inhibited and go into the high impedance state.

The individual address lines permit direct acquisition of data stored in any four of the latches. Four individual decoding gates are used to complete the address for reading a word. When the read address is made in conjunction with the read-enable signal, the word appears at the four outputs.

This arrangement-data entry addressing separate from data read addressing and individual sense line — elimi-

nates recovery times, permits simultaneous reading and writing, and is limited in speed only by the write time (27 ns typical) and the read time (24 ns typical). The register file has a non-volatile readout in that data is not lost when addressed.

All inputs (except read enable and write enable) are buffered to lower the drive requirements to one normal Series DM74LS load, and input clamping diodes minimize switching transients to simplify system design. High speed, double ended AND-OR-INVERT gates are employed for the read-address function and have high sink current, 3-STATE outputs. Up to 128 of these outputs may be wire-AND connected for increasing the capacity up to 512 words. Any number of these registers may be paralleled to provide nbit word length.

#### Features

# **Function Tables**

DM74LS670

Write Table (Note 1)(Note 2)

|   | Wr     | ite Inp        | uts            |                       | We                    | ord                   |                |

|---|--------|----------------|----------------|-----------------------|-----------------------|-----------------------|----------------|

|   | WB     | W <sub>A</sub> | G <sub>W</sub> | 0                     | 1                     | 2                     | 3              |

|   | L      | L              | L              | Q = D                 | <b>Q</b> <sub>0</sub> | <b>Q</b> <sub>0</sub> | Q <sub>0</sub> |

|   | L      | н              | L              | $Q_0$                 | Q = D                 | $Q_0$                 | $Q_0$          |

|   | н      | L              | L              | $Q_0$                 | $Q_0$                 | Q = D                 | $Q_0$          |

|   | н      | н              | L              | $Q_0$                 | $Q_0$                 | $Q_0$                 | Q = D          |

|   | Х      | Х              | н              | <b>Q</b> <sub>0</sub> | <b>Q</b> <sub>0</sub> | <b>Q</b> <sub>0</sub> | $Q_0$          |

| Н | = HIGH | Level          |                | L = LOW               | Level                 | X = D                 | on't Care      |

| Read | Table | (Note 3)  |

|------|-------|-----------|

|      | IGNIO | (11010 0) |

| Read Inputs                                  |   |    | Outputs |      |      |      |  |  |  |

|----------------------------------------------|---|----|---------|------|------|------|--|--|--|

| R <sub>B</sub> R <sub>A</sub> G <sub>R</sub> |   | Q1 | Q2      | Q3   | Q4   |      |  |  |  |

| L                                            | L | L  | WOB1    | WOB2 | WOB3 | WOB4 |  |  |  |

| L                                            | н | L  | W1B1    | W1B2 | W1B3 | W1B4 |  |  |  |

| н                                            | L | L  | W2B1    | W2B2 | W2B3 | W2B4 |  |  |  |

| Н                                            | н | L  | W3B1    | W3B2 | W3B3 | W3B4 |  |  |  |

| Х                                            | Х | н  | Z       | Z    | Z    | Z    |  |  |  |

Z = High Impedance (OFF) Note 1: (Q = D) = The four selected internal flip-flop outputs will assume the states applied to the four external data inputs.

Note 2:  $Q_0 =$  The level of Q before the indicated input conditions were established.

Note 3: WOB1 = The first bit of word 0, etc.

www.fairchildsemi.com

2

#### Absolute Maximum Ratings(Note 4)

| Supply Voltage                       | 7V                                |

|--------------------------------------|-----------------------------------|

| Input Voltage                        | 7V                                |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$    |

| Storage Temperature Range            | $-65^{\circ}C$ to $+150^{\circ}C$ |

**Note 4:** The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# DM74LS670

### **Recommended Operating Conditions**

| Symbol             | Parameter                                        |  | Min  | Nom | Max  | Units |

|--------------------|--------------------------------------------------|--|------|-----|------|-------|

| V <sub>CC</sub>    | Supply Voltage                                   |  | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub>    | HIGH Level Input Voltage                         |  | 2    |     |      | V     |

| V <sub>IL</sub>    | LOW Level Input Voltage                          |  |      |     | 0.8  | V     |

| I <sub>OH</sub>    | HIGH Level Output Current                        |  |      |     | -2.6 | mA    |

| I <sub>OL</sub>    | LOW Level Output Current                         |  |      |     | 24   | mA    |

| t <sub>W</sub>     | Write Enable Pulse Width (Note 5)                |  | 25   |     |      | ns    |

| t <sub>SU</sub>    | Setup Time Data                                  |  | 10   |     |      | ns    |

|                    | (Note 5)(Note 6) W <sub>A</sub> , W <sub>B</sub> |  | 15   |     |      |       |

| t <sub>H</sub>     | Hold Time Data                                   |  | 15   |     |      | ns    |

|                    | (Note 5)(Note 6) W <sub>A</sub> , W <sub>B</sub> |  | 5    |     |      |       |

| t <sub>LATCH</sub> | Latch Time for New Data (Note 5)(Note 7)         |  | 25   |     |      | ns    |

| T <sub>A</sub>     | Free Air Operating Temperature                   |  | 0    |     | 70   | °C    |

Note 5:  $T_A$  = 25°C and  $V_{CC}$  = 5V.

Note 6: Times are with respect to the Write-Enable input. Write-Select time will protect the data written into the previous address. If protection of data in the previous address,  $t_{ETUP}$  ( $W_A$ ,  $W_B$ ) can be ignored. As any address selection sustained for the final 30 ns of the Write-Enable pulse and during  $t_{H}$  ( $W_A$ ,  $W_B$ ) will result in data being written into that location. Depending on the duration of the input conditions, one or a number of previous addresses may have been written into.

Note 7: Latch time is the time allowed for the internal output of the latch to assume the state of new data. This is important only when attempting to read from a location immediately after that location has received new data.

# **Electrical Characteristics**

| Symbol           | Parameter                         | Condition                            | s              | Min | Typ<br>(Note 8) | Max  | Units |

|------------------|-----------------------------------|--------------------------------------|----------------|-----|-----------------|------|-------|

| VI               | Input Clamp Voltage               | $V_{CC} = Min, I_I = -18 \text{ mA}$ |                |     |                 | -1.5 | V     |

| V <sub>OH</sub>  | HIGH Level                        | $V_{CC} = Min, I_{OH} = Max$         |                | 2.4 | 3.4             |      | v     |

|                  | Output Voltage                    | $V_{IL} = Max, V_{IH} = Min$         |                | 2.4 | 3.4             |      | v     |

| V <sub>OL</sub>  | LOW Level                         | $V_{CC} = Min, I_{OL} = Max$         |                |     | 0.34            | 0.5  | V     |

|                  | Output Voltage                    | $I_{OL} = Max, V_{IH} = Min$         |                |     | 0.34            | 0.5  | v     |

| l <sub>l</sub>   | Input Current @ Max               | V <sub>CC</sub> = Max                | D, R or W      |     |                 | 0.1  |       |

|                  | Input Voltage                     | $V_I = 7V$                           | G <sub>W</sub> |     |                 | 0.2  | mA    |

|                  |                                   |                                      | G <sub>R</sub> |     |                 | 0.3  |       |

| I <sub>IH</sub>  | HIGH Level                        | V <sub>CC</sub> = Max                | D, R or W      |     |                 | 20   |       |

|                  | Input Current                     | $V_{I} = 2.7V$                       | G <sub>W</sub> |     |                 | 40   | μΑ    |

|                  |                                   |                                      | G <sub>R</sub> |     |                 | 60   |       |

| Ι <sub>ΙL</sub>  | LOW Level                         | V <sub>CC</sub> = Max                | D, R or W      |     |                 | -0.4 |       |

|                  | Input Current                     | $V_I = 0.4V$                         | G <sub>W</sub> |     |                 | -0.8 | mA    |

|                  |                                   |                                      | G <sub>R</sub> |     |                 | -1.2 |       |

| I <sub>OZH</sub> | Off-State Output Current with     | $V_{CC} = Max, V_O = 2.7V$           |                |     |                 | 20   |       |

|                  | HIGH Level Output Voltage Applied | $V_{IH} = Min, V_{IL} = Max$         |                |     | 20              | 20   | μA    |

| l <sub>ozl</sub> | Off-State Output Current with     | $V_{CC} = Max, V_O = 0.4V$           |                |     |                 | -20  | μA    |

|                  | LOW Level Output Voltage Applied  | $V_{IH} = Min, V_{IL} = Max$         |                |     |                 | -20  | μΑ    |

| l <sub>os</sub>  | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 9)       |                | -20 |                 | -100 | mA    |

| I <sub>CC</sub>  | Supply Current                    | V <sub>CC</sub> = Max (Note 10)      |                |     | 30              | 50   | mA    |

Note 8: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 9: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 10: I<sub>CC</sub> is measured with 4.5V applied to all DATA inputs and both ENABLE inputs, all ADDRESS inputs are grounded and all outputs are OPEN.

#### **Switching Characteristics**

at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$

|                  |                             | From (Input)           | $R_L = 667\Omega$      |    |                         |    |       |

|------------------|-----------------------------|------------------------|------------------------|----|-------------------------|----|-------|

| Symbol           | Parameter                   |                        | C <sub>L</sub> = 45 pF |    | C <sub>L</sub> = 150 pF |    | Units |

|                  |                             | To (Output)            | Min Max                |    | Min Max                 |    |       |

| t <sub>PLH</sub> | Propagation Delay Time      | Read Select to Q       |                        | 40 |                         | 50 |       |

|                  | LOW-to-HIGH Level Output    | Read Select to Q       |                        | 40 | 50                      |    | ns    |

| t <sub>PHL</sub> | Propagation Delay Time      | Read Select to Q       |                        | 45 |                         | 55 |       |

|                  | HIGH-to-LOW Level Output    | Read Select to Q       | 45                     |    | 55                      |    | ns    |

| t <sub>PLH</sub> | Propagation Delay Time      | Write Enable to Q      |                        | 45 |                         | 55 | ns    |

|                  | LOW-to-HIGH Level Output    |                        | 45                     |    | 55                      |    | 115   |

| t <sub>PHL</sub> | Propagation Delay Time      | Write Enable to Q      |                        | 50 |                         | 60 | ns    |

|                  | HIGH-to-LOW Level Output    | While Linable to Q     |                        | 50 |                         |    |       |

| t <sub>PLH</sub> | Propagation Delay Time      | Data to Q              |                        | 45 |                         | 55 | ns    |

|                  | LOW-to-HIGH Level Output    | Data to Q              |                        |    |                         |    | 113   |

| t <sub>PHL</sub> | Propagation Delay Time      | Data to Q              |                        | 40 |                         | 50 | ns    |

|                  | HIGH-to-LOW Level Output    | Data to Q              | 40                     |    | 00                      |    | 113   |

| t <sub>PZH</sub> | Output Enable Time          | Read Enable to Any Q   |                        | 35 |                         | 45 | ns    |

|                  | to HIGH Level Output        | Read Linable to Arry Q |                        |    | 45                      |    | 115   |

| t <sub>PZL</sub> | Output Enable Time          | Read Enable to Any Q   |                        | 40 |                         | 50 | ns    |

|                  | to LOW Level Output         | Read Linable to Arry Q |                        | 40 |                         | 50 |       |

| t <sub>PHZ</sub> | Output Disable Time from    | Read Enable to Any Q   |                        | 50 |                         |    | ns    |

|                  | HIGH Level Output (Note 11) | Read Enable to Arry Q  |                        | 50 |                         |    |       |

| t <sub>PLZ</sub> | Output Disable Time from    | Read Enable to Any Q   |                        | 35 | 25                      |    | ns    |

|                  | LOW Level Output (Note 11)  | Read Enable to Any Q   |                        | 30 |                         |    | 115   |

DM74LS670

www.fairchildsemi.com

www.fairchildsemi.com